# 67B Hall Effect Joystick I2C User Manual

### 1 Introduction

The 67B joystick is a proportional output joystick which provides an X,Y coordinate (0-50) proportional to the joystick location. The X,Y coordinates are read from the joystick via an I<sup>2</sup>C bus. Features include:

- Proportional Joystick

- I<sup>2</sup>C Interface (other interfaces available)

- Low Operating Current (3 mA, max.@ V<sub>DD</sub> = 3.3V)

- Low Power "Sleep Mode" (110  $\mu$ A, max. @  $V_{DD}$  = 3.3V)

- Push button and 3 Position Momentary (Rotary) Switch options available.

#### 2 Hardware Interface

**2.1 Connector -** Two options are available – header or ribbon cable with connector.

A. Ribbon cable with Molex 14-56-2084 connector (Mates with Molex 70543 Series headers or standard 0.100" pin headers with 0.025" sq. pins).

B. Header (1x8) - 0.10" centers with 0.025" sq. pins.

| Pin# | Signal   | 1/0 | Description                                           |

|------|----------|-----|-------------------------------------------------------|

| 1    | $V_{DD}$ | ı   | Power Supply                                          |

| 2    | SDA      | 1/0 | I <sup>2</sup> C Data Line                            |

| 3    |          |     | Spare                                                 |

| 4    | INTn     | Out | Interrupt Out (Open Drain. Active Low)                |

| 5    | PBn      | Out | Pushbutton Out (Open Drain – Active Low) if installed |

| 6    | A1       | In  | A1 (LSB) of 7 bit I <sup>2</sup> C address            |

| 7    | SCL      | In  | I <sup>2</sup> C Clock Line                           |

| 8    | $V_{SS}$ | -   | Ground                                                |

**Table 1-67B Connector Signals**

The 67B is an  $I^2$ C (Slave) with 7 bit  $I^2$ C address of 42h (A1n floating) or 40h (A1n tied to Gnd).  $I^2$ C speed: up to 400 KHz.

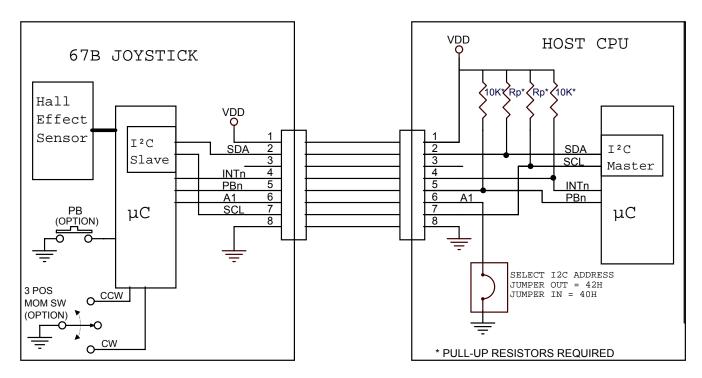

External pull-up resistors are required for I<sup>2</sup>C signals (SDA & SCL- See Sec 2.3 for recommended pull-up resistors for I<sup>2</sup>C signals), INTn and PBn (Recommended value 2K-10K). (See Figure 1)

INTn – Interrupt Out (Active Low) - Goes low only when a different X, Y value is available, or for units with a switch option, if a switch position has changed. Reading the Y value causes INTn to go high (inactive). For most efficient use of the I<sup>2</sup>C bus and processor resources it is recommended that the INTn signal be used to trigger reading of the X, Y value from the joystick. If INTn is not used, X, Y values should be read continuously at a rate of 50 samples/sec. An external pull-up resistor in the range of 2K - 10K (see Figure 1) is required for INTn.

Figure 1 - 67B Electrical Connection Diagram

# 2.2 Cable/PCB Trace Length

Cable/PCB Trace Length: Varies with I<sup>2</sup>C frequency. The I<sup>2</sup>C Spec. specifies a maximum capacitance per signal line (SCL or SDA) of 400 pF. The bus capacitance is the total of wire, PCB traces and pins. The longer the cable/PCB trace length the higher the bus capacitance and thus, the lower the operating frequency that can be used.

## 2.3 Pull-up Resistors

#### 2.3.1 I<sup>2</sup>C Signals (SCL, SDA) Pull-up Resistors

The two I<sup>2</sup>C signals (SDA & SCL) must be pulled up to the power supply voltage at the Host CPU. The pull-up resistor value depends on the bus capacitance and SCL frequency. See Table 2 below for recommended pull-up resistor values vs. SCL frequency and bus capacitance:

|                         | Rp recommended       |        |        |        |  |  |  |

|-------------------------|----------------------|--------|--------|--------|--|--|--|

|                         | Bus Load Capacitance |        |        |        |  |  |  |

| SCL Frequency           | 100 pF               | 200 pF | 300 pF | 400 pF |  |  |  |

| Standard Mode (100 KHz) | 6.49ΚΩ               | 3.48ΚΩ | 2.49ΚΩ | 2ΚΩ    |  |  |  |

| Fast Mode (400 KHz)     | 2.26ΚΩ               | 1.4ΚΩ  | 1.1ΚΩ  |        |  |  |  |

Table 2 - Recommended Pull-up Resistors for SCL, SDA vs. Frequency & Bus Capacitance

To determine if a proper pull-up value is being check the low and high voltage levels for SCL and SDA during I<sup>2</sup>C bus activity. The signal levels should meet the following requirements with at least a 0.1V margin:

$$V_{L, MAX} < 0.3 V_{DD} V_{H, MIN} > 0.7 V_{DD}$$

For more on choosing the I<sup>2</sup>C pull-up resistors see: Sec. 7.1 in *I2C-bus specification and user manual, Rev.* 03 (NXP UM10204).

#### 2.3.2 INTn and Pushbutton (PBn) Pull-up Resistor

The pull-up for the INTn and Pushbutton (if installed) signals should be between 2K-10KΩ.

# 3 I<sup>2</sup>C Interface

The 67B joystick communicates over an I<sup>2</sup>C bus (2-wire bi-directional serial interface). The host CPU (master) must initiate the data transfers, as the 67B is a slave device.

**I²C address** - The I²C address consists of 7 bits (D7-D1) and a bit (D0) indicating whether it is a Read (1) or Write (0) cycle. The 67B is shipped from the factory with the 7-bit device I²C address of 42H ('0100 001X') when A1 (pin 6) is left floating (not connected). The I²C address may be changed to 40H ('0100 000X) by pulling A1n to Gnd. If A1n is changed after power-up then a reset command needs to be sent to the joystick to make active the new value (A1n is only read by the joystick after a power-up or reset command). Changing the I²C address would be necessary if two 67B joysticks are connected to the same I²C bus or if another component connected to the I²C bus shared the same I²C address. To request a custom I²C address contact Grayhill.

SDA is a bi-directional signal and is used to read and write the serial data. The SCL signal is the clock generated by the host CPU, to synchronize the SDA data in read and write mode. The maximum I<sup>2</sup>C clock frequency is 400 KHz with data triggered on the rising edge of SCL.

Clock Stretching - Clock stretching occurs when a device on the bus holds the SCL line low effectively pausing communication. The joystick (slave) may stretch the clock to allow more time to load data to be read by the master device. It is important that the I<sup>2</sup>C Master interfacing with the 67B implement clock stretching on a byte level for reliable operation with the joystick. See Sec 5.1.1 for more on clock stretching.

# 3.1 I<sup>2</sup>C Registers

#### 3.1.1 X Register

| Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|-----------|----------|-------|-------|-------|-------|-------|----------|

| X(7) sign | X(6) MSB | X(5)  | X(4)  | X(3)  | X(2)  | X(1)  | X(0) LSB |

| R         | R        | R     | R     | R     | R     | R     | R        |

Reset value: 0000 0000

• Bit7-0: X coordinate

X coordinate, 2's complement format (signed –50 to +50).

Note: After every complete I<sup>2</sup>C transaction the register pointer in the joystick is set to point at the X register so that X register value can be read without writing to register pointer (See Sec 3.2).

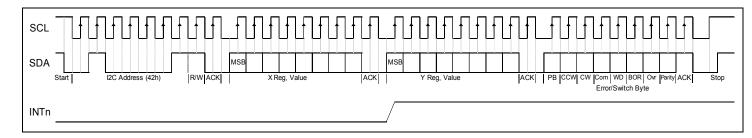

IMPORTANT: In order to keep X & Y values paired together or "in synch.", X register data should be read in an I2C sequence which reads both the X & Y registers as described in Sec. 3.2.1 and Figure 2.

#### 3.1.2 Y Register

| Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|-----------|----------|-------|-------|-------|-------|-------|----------|

| Y(7) sign | Y(6) MSB | Y(5)  | Y(4)  | Y(3)  | Y(2)  | Y(1)  | Y(0) LSB |

| R         | R        | R     | R     | R     | R     | R     | R        |

Reset value: 0000 0000

#### · Bit7-0: Y coordinate

Y coordinate, 2's complement format (signed –50 to +50)

Reading the Y register will reset INTn output to Hi-Z.

The Y register should be read in a single I<sup>2</sup>C sequence that reads the X Register first immediately followed by the Y register as described in Sec. 3.2.1 and Figure 2.

#### 3.1.3 Error/Switch Register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|-------|-------|-------|-------|-------|-------|-------|--------|

| PB    | CCW   | CW    | Com   | WD    | BOR   | Ovr   | Parity |

| R     | R     | R     | R     | R     | R     | R     | R      |

X = Do Not Care

Reset value: 0000 000X

When the Ext. Host (I<sup>2</sup>C Master) executes a 3 byte I<sup>2</sup>C read sequence the 3<sup>rd</sup> byte read is the Error/Switch byte. This byte contains bits which indicate joystick errors and bits which indicate the switch positions (if installed).

D0 – Parity – The joystick generates a parity bit for the 3 data bytes of the I<sup>2</sup>C message. Odd parity is used. (Read Only)

D1 – Overrun (Ovr) – When this bit is set (1) indicates that X or Y data has changed before it was read. This error indicates that the Ext. Host is not reading the data at a fast enough rate (up to 50 samples/sec.). Reading the Error/Switch byte clears this bit. (Read Only).

D2 – (BOR) Brown-Out Reset indicator (1 = Brown Out occurred) Indicates that supply voltage dropped to below brownout threshold voltage (2.7V) and caused a joystick reset. Cleared by reset of joystick. (Read Only).

D3 - (WD) Watchdog Timer time out indicator (1 = time out occurred). Joystick internal program malfunction caused a reset. Cleared by reset of joystick. (Read Only).

D4 – (Com) Internal Communication Error - When set (1) indicates that an internal comm. error occurred when the joystick microcontroller tried to read or write to the Hall Sensor. Cleared by reset of joystick. (Read Only).

D5 – Clockwise (CW) (if option installed) – The internal microcontroller reads the 3 Position Momentary Switch and debounces the signal. When active (1) indicates the switch is in the Clockwise (CW) position. (if option not installed – set to 0). (Read Only).

D6 – Counter-Clockwise (CCW) (if option installed) – The internal microcontroller reads the 3 Position Momentary Switch and debounces the signal. When active (1) indicates the switch is in the Counter Clockwise (CCW) position. (if option not installed – set to 0). (Read Only).

D7 – Pushbutton (PB) (if option installed) – The internal microcontroller reads the pushbutton and debounces the signal. When active (1) indicates that the pushbutton has been pressed (if option not installed – set to 0). (Read Only).

### 3.1.4 Control Register (76h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| X     | Х     | Х     | Х     | Х     | Х     | Reset | Х     |

|       |       |       |       |       |       | W     |       |

X = Do Not Care

Reset value: 1001 1010 (9Ah)

Writing to this register with Reset (Bit 1) high resets joystick and sets all registers to default values. The Reset bit is set low by the joystick after completing the reset sequence. Note: there is a start-up time  $(T_{P,W})$  which must be observed after resetting the joystick.

# 3.2 I<sup>2</sup>C Read and Write Cycles

**3.2.1** Read X, Y and Error/Switch Bytes – When INTn goes low there are new X & Y values available. To read the three bytes the external I<sup>2</sup>C Master should perform a read sequence of 3 bytes <u>without</u> providing a register address (Joystick always sends X register value followed by Y register value and then the Error/Switch byte for any 3 byte read without a register address). INTn will go high (inactive) at the beginning of the read of the Y value (see Figure 2).

I<sup>2</sup>C Start Command

41h or 43h (Joystick I<sup>2</sup>C Address with D0 set for read)

X Byte (Data from Joystick)

Y Byte (Data from Joystick)

Error/Switch Byte (Data from Joystick)

I<sup>2</sup>C Stop Command

<u>Important Note</u>: If a new X & Y value is available before the previous values are read the new values will over-write the old (with the loss of the oldest values). However, in order to keep the X & Y values paired together or "in sync", <u>it is important that the user read the X, Y and Error/Switch bytes in the a single I<sup>2</sup>C sequence as shown in Figure 2. This is also the fastest and most efficient use of the I<sup>2</sup>C bus.</u>

Figure 2 – Read X, Y & Error/Switch Bytes over I2C Bus

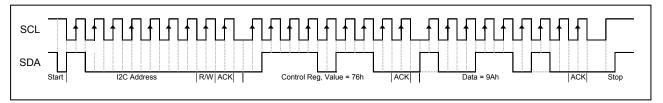

**3.2.2** Reset Joystick – To reset the joystick the I<sup>2</sup>C Master should perform a write sequence of 1 byte and must provide the register address for Control Reg. :

I<sup>2</sup>C Start Command 40h or 42h (Joystick I<sup>2</sup>C Address with D0 low for write) 76h (Register Address for Control Reg.) 9Ah (Data) I<sup>2</sup>C Stop Command

Note: after sending the reset command the  $I^2C$  Master must wait 300 ms before attempting to access the 67B. At the end of the Nominal Startup Time ( $T_{P,W}$ ) the 67B generates the first XY pair of values and sets INTn low. Thereafter INTn goes low only if the X or Y value changes.

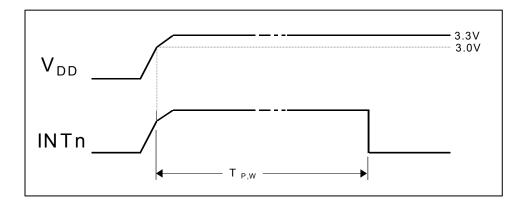

Figure 3 – Send Reset Command over I<sup>2</sup>C Bus

# 4 Power Modes & Sleep Threshold

**4.1 Power-Up Sequence** – During a power-up once the power supply voltage reaches 3.0V the user must wait the Nominal Startup Time (T<sub>P,W)</sub> before communicating with the joystick over the I<sup>2</sup>C bus (also applies to a reset joystick command). At the end of the Nominal Wakeup Time the 67B generates the first pair of XY values and sets INTn low. Thereafter INTn goes low only if the X or Y value changes or for cases with a switch option, if a switch position has changed.

Figure 4 – Power-Up Sequence

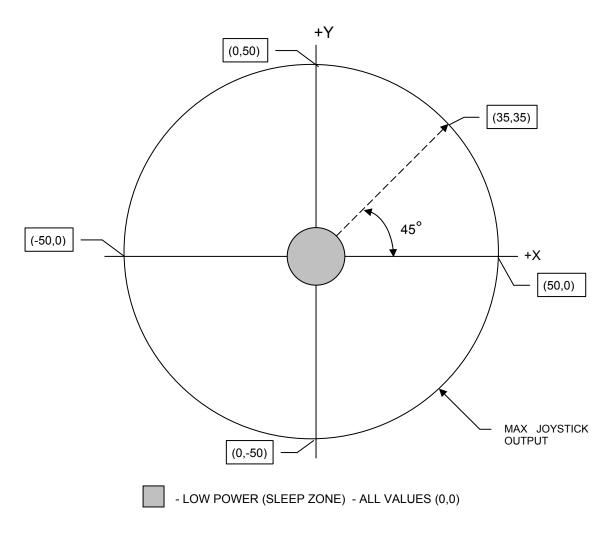

- **4.2 Low Power (Sleep) Mode:** When the joystick position is within a circle defined as the Sleep Zone for ten consecutive measurements the joystick goes to the Low Power mode where power consumption is significantly lower. The Sleep Zone typically extends to a joystick shaft angle of 5° from the center (See Figure **6**). The last XY value output before entering the Low Power mode is (0,0). As long as the joystick remains within the Sleep Zone circle, it will remain in the Low Power Mode and INTn will stay in the float state. Low Power (Sleep Mode) current may be higher if supply voltage drops below 2.0V.

- **4.3 Full Power Mode:** When the joystick position is moved outside of the Low Power (Sleep) zone the joystick switches to the Full Power Mode where an <u>internal</u> measurement occurs every 20 ms. If either the X or Y value changes from the last values measured, the INTn output (Pin 5) is set low signaling new X & Y values are ready to be read. INTn is cleared (Hi-Z) while the Y value is read. Power consumption is higher in this mode.

Figure 5 - Sleep Zone & Max Output Circle

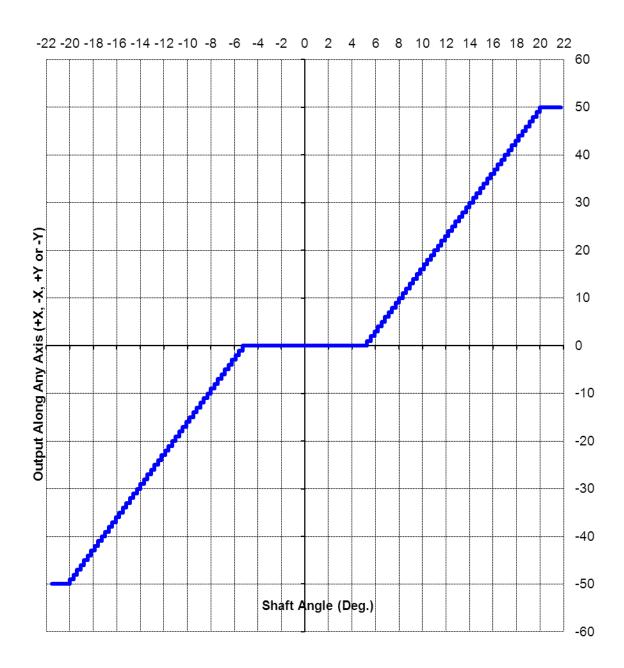

Figure 6 – Joystick Output Along X or Y Axis vs. Shaft Angle (Typical)

# **5 SPECIFICATIONS**

NOTICE: Stresses above those listed under "Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device above those listed in the operation listings of this specification is not implied. Exposure above maximum ratings conditions for extended periods may affect device reliability.

**Table 3- Absolute Maximum Ratings (non operating)**

| Parameter                                     | Sym.              | Min  | Max            | Unit | Note |

|-----------------------------------------------|-------------------|------|----------------|------|------|

| DC Supply Voltage                             | $V_{DD}$          | -0.3 | 4.0            | V    |      |

| Voltage on all other pins with respect to Vss | $V_{IN}$          | -0.3 | $V_{DD} + 0.3$ | V    |      |

| Max current sunk by any I/O pin               |                   |      | 25             | mA   |      |

| Storage temperature                           | T <sub>strg</sub> | -55  | +100           | °C   |      |

**Table 4 - Operating Conditions**

| Parameter                                                                               | Sym.                    | Min                           | Тур | Max                  | Unit            | Note                                                                                 |

|-----------------------------------------------------------------------------------------|-------------------------|-------------------------------|-----|----------------------|-----------------|--------------------------------------------------------------------------------------|

| DC Supply Voltage                                                                       | $V_{DD}$                | 3.0                           | 3.3 | 3.6                  | V               |                                                                                      |

|                                                                                         |                         | 0.7 V <sub>DD</sub>           |     |                      | V               | SCL, SDA                                                                             |

| High level input voltage                                                                | V <sub>IH</sub>         | 0.25 V <sub>DD</sub><br>+ 0.8 |     |                      | V               | A1                                                                                   |

| Low level input voltage                                                                 | V                       |                               |     | $0.3 V_{DD}$         | V               | SCL, SDA                                                                             |

| Low level input voltage                                                                 | V <sub>IL</sub>         |                               |     | 0.15 V <sub>DD</sub> | V               | A1n                                                                                  |

| Leakage Current                                                                         | I <sub>IL</sub>         | -                             | ±5  | ±125                 | nA              | V <sub>SS</sub> ≤ V <sub>PIN</sub> ≤ V <sub>DD</sub> , Pin at high impedance at 85°C |

| Low level output voltage                                                                | $V_{OL}$                |                               |     | 0.6                  | V               | INTn , SDA<br>$I_{OL}$ = 6mA, $V_{DD}$ = 3.30V                                       |

| Current Consumption, Full Power mode (Average current V <sub>DD</sub> pin)              | I <sub>DD1</sub>        |                               | 2.5 | 3.0                  | mA              | V <sub>DD</sub> = 3.30V, Note 1                                                      |

| Current Consumption, Low Power (sleep) mode (Average current V <sub>DD</sub> pin)       | I <sub>DD2</sub>        |                               | 50  | 110                  | μA              | V <sub>DD</sub> = 3.30V. Notes 1, 3                                                  |

| Current Consumption (with Mom.<br>Turn Option) (Average current V <sub>DD</sub><br>pin) | I <sub>DD3</sub>        |                               | 4.0 | 6.0                  | mA              | V <sub>DD</sub> = 3.30V. Notes 1, 5.                                                 |

| Measurement Frequency, (Full Power mode)                                                |                         |                               | 50  |                      | Sample<br>s/sec |                                                                                      |

| Response Time (Full Power Mode)                                                         |                         |                               |     | 20                   | ms              | Note 2                                                                               |

| Response Time (Low Power Mode)                                                          |                         |                               |     | 80                   | ms              | Note 2                                                                               |

| Output with Max. Joystick Deflection                                                    | $X_{MAX}$ or $Y_{MAX}$  | ±49                           | ±50 | ±50                  | Units           | Notes 4, 6                                                                           |

| Output with Joystick Released (Center)                                                  | $X_{MIN,}$ or $Y_{MIN}$ | -                             | 0   | 0                    | Units           |                                                                                      |

| Low Power (Sleep) Threshold                                                             |                         |                               | 5   |                      | Deg.            |                                                                                      |

| Nominal Startup Time                                                                    | $T_{P,W}$               |                               |     | 300                  | ms              |                                                                                      |

| Operating temperature range                                                             | T <sub>amb</sub>        | -40                           |     | +85                  | °C              |                                                                                      |

Note 1: Measured with SDA, SCL, INTn and PBn terminated with pull-up resistors (See Sec 2.3). Does not include current in external pull-up resistors.

- Note 2: Response time is the time from joystick movement to when new X,Y position data is available (INTn goes low).

- Note 3: For VDD < 2.0V current will exceed 110  $\mu$ A.

- Note 4: Maximum values along X or Y axis in positive and negative directions.

- Note 5: Full Power Mode Only (No sleep mode with 3 Pos. Mom. Sw Option).

Note 6: Positive value is for movement in the positive X or Y direction. Negative value is for movement in the negative X or Y direction. Moving the joystick toward the cable will result in positive Y values.

# 5.1 I<sup>2</sup>C Bus Timing Requirements

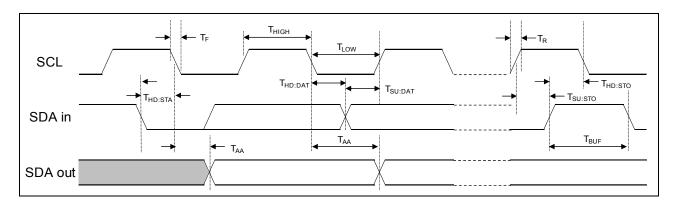

Figure 7 - I<sup>2</sup>C Bus Data Requirements

Table 5 - I<sup>2</sup>C Bus Data Requirements

| Parame                             | eter               | Sym.     | Min        | Тур | Max  | Unit | Note                                 |

|------------------------------------|--------------------|----------|------------|-----|------|------|--------------------------------------|

| Start condition                    | 100 kHz mode       | T HD:STA | 4000       | _   | _    |      | After this period, the first clock   |

| Hold time                          | 400 kHz mode       | I HD:STA | 600        | _   | _    | ns   | pulse is generated                   |

| Stop condition                     | 100 kHz mode       | T su:sto | 4700       |     | _    | ns   |                                      |

| Setup time                         | 400 kHz mode       | 1 50.510 | 600        |     | _    | 115  |                                      |

| Stop condition                     | 100 kHz mode       | T HD:STO | 4000       | _   | _    | 20   |                                      |

| Hold time                          | 400 kHz mode       | I HD:210 | 600        | _   | _    | ns   |                                      |

| Clask high time                    | 100 kHz mode       | Turou    | 4.0        | _   | _    | _    |                                      |

| Clock high time                    | 400 kHz mode       | T нідн   | 0.6        | _   | _    | μS   |                                      |

| Clock low time                     | 100 kHz mode       | T LOW    | 4.7        | _   | _    | _    |                                      |

| Clock low time                     | 400 kHz mode       | I LOW    | 1.3        | _   | _    | μS   |                                      |

| SDA and SCL rise                   | 100 kHz mode       |          | _          | _   | 1000 | ns   |                                      |

| time                               | 400 kHz mode       | Tr       | 20 + 0.1CB | _   | 300  |      | CB is specified to be from 10-400 pF |

| SDA and SCL fall                   | 100 kHz mode       | TF       | _          | _   | 250  | ns   |                                      |

| time                               | 400 kHz mode       |          | 20 + 0.1CB | 1   | 250  |      | CB is specified to be from 10-400 pF |

| Data input hold time               | 100 kHz mode       | T HD:DAT | 0          |     | _    | ns   |                                      |

| Data input noid time               | 400 kHz mode       | I HD:DAT | 0          | _   | 0.9  | μS   |                                      |

| Data input setup                   | 100 kHz mode       | T SU:DAT | 250        | _   | _    | ns   | (Note 2)                             |

| time                               | 400 kHz mode       | I SU:DAT | 100        | _   | _    | ns   |                                      |

| Output valid from                  | 100 kHz mode       | T AA     | _          | _   | 3.5  | μS   | (Note 1)                             |

| clock                              | 400 kHz mode       | I AA     | _          | _   | _    | ns   |                                      |

| Bus free time                      | 100 kHz mode       | _        | 4.7        | _   | _    |      | Time the bus must be free            |

|                                    | 400 kHz mode       | T BUF    | 1.3        | _   | _    | μS   | before a new transmission can start  |

| SCL delay from<br>Clock Stretching | Full Power<br>Mode | T DEL    | _          | 20  | _    | 6    |                                      |

|                                    | Low Power<br>Mode  | I DEL    |            | 45  | _    | μS   | See Figure 8                         |

| Bus capacitive loading             |                    | Св       | _          | _   | 400  | pF   |                                      |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

Note 2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT  $\geq$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

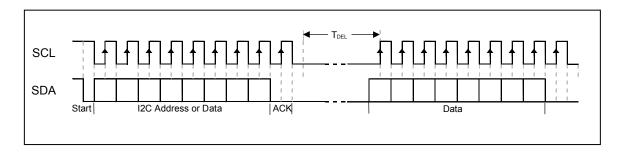

#### 5.1.1 Clock Stretching

As mentioned previously the I<sup>2</sup>C Master that interfaces with the joystick must be capable of clock stretching on a byte level. The joystick is able to transmit a byte of data at a fast rate, but may need more time to prepare the next byte to be transmitted. The joystick (slave) holds the SCL line LOW after transmission and acknowledgment of a byte to force the master into a wait state until the slave is ready for the next byte transfer in a type of handshake procedure (See Figure 8 below). See I<sup>2</sup>C Spec. UM10204, Rev. 3, Sec. 3.9 for more on clock stretching.

Figure 8 - Clock Stretching by Joystick

# **Revision History**

| Date     | Rev | Name | Description of Changes                                                                                                                                                                                                                                                |

|----------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06/20/13 | 1.0 | SAK  | Initial Version                                                                                                                                                                                                                                                       |

| 09/18/13 | 1.1 | SAK  | In Table 4 Changed Operating Temp to be one operating temp for all versions (-40 to +85 °C).  Added Figure 6 (Angle v Output graph).  In Table 4 added current (I <sub>DD3</sub> ) for joystick with 3 Pos. Mom. Sw. option.                                          |

| 09/24/13 | 1.2 | SAK  | In Table 4 added current spec for 5V version of joystick with 3 Position Momentary Switch option.                                                                                                                                                                     |

| 12/10/13 | 1.3 | SAK  |                                                                                                                                                                                                                                                                       |

| 02/17/14 | 1.4 | SAK  | In Sec 3.1.1 and 3.1.2 changed X & Y value range to 50 (was 40). In Table 4 added Typ. & Max current for 3.3V joystick with 3 Position Mom. Sw. (I <sub>DD2</sub> ). In Table 4 added new Note 1 and changed old Note 1 to Note 6. Removed all references to 5V unit. |